imec présente des mémoires DRAM sans condensateur

gtag(‘js’, new Date()); gtag(‘config’, ‘UA-160857065-1’);

Imec a développé une architecture de cellule de mémoire DRAM qui élimine le condensateur et peut donc être empilée dans une structure 3D.

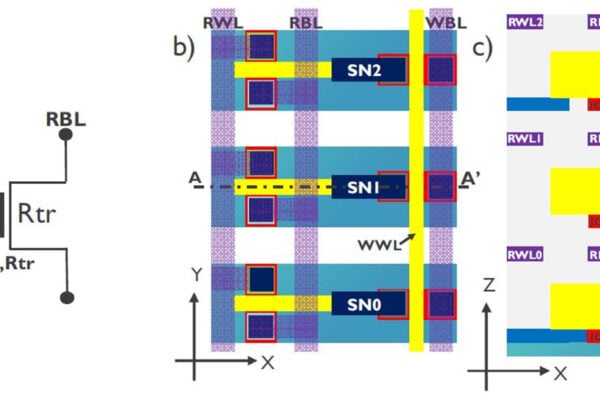

Les conceptions DRAM classiques au-delà de 32 Go ont du mal à évoluer à mesure qu’elles deviennent plus petites, en grande partie à cause de la présence de condensateurs. Au lieu de cela, imec a montré une conception avec deux transistors à couches minces à faible consommation d’indium-gallium-oxyde de zinc (IGZO-TFT) et sans condensateur de stockage. Les IGZO-TFT sont bien connus pour leur très faible courant à l’arrêt, et la capacité parasite du transistor de lecture sert d’élément de stockage.

La cellule 2T0C ( 2 transistors, 0 condensateur) a un temps de rétention supérieur à 400 s, ce qui réduit encore la consommation d’énergie avec un taux de rafraîchissement beaucoup plus long. Cela peut être implémenté sur le back-end d’un processus CMOS (BEOL) pour placer des couches de mémoire dynamique au-dessus de la logique.

Imec a construit les transistors avec une géométrie de 45 nm sur des plaquettes de 300 mm et décrit l’architecture dans un article lors de la conférence IEDM cette semaine, en décembre 2020.

«Outre le long temps de rétention, les cellules DRAM basées sur IGZO-TFT présentent un deuxième avantage majeur par rapport aux technologies DRAM actuelles. Contrairement au silicium, les transistors IGZO-TFT peuvent être fabriqués à des températures relativement basses et sont donc compatibles avec le traitement BEOL », a déclaré Gouri Sankar Kar, directeur du programme chez imec.

«Cela nous permet de déplacer la périphérie de la cellule mémoire DRAM sous la matrice mémoire, ce qui réduit considérablement l’encombrement de la puce mémoire. De plus, le traitement BEOL ouvre des voies vers l’empilement de cellules DRAM individuelles, permettant ainsi des architectures 3D-DRAM. »

145 milliards d’euros pour l’industrie des semiconducteurs en Europe

La mise à l’échelle de la mémoire DRAM est un élément clé pour le cloud computing et l’IA, qui sont des domaines que la Commission européenne a identifiés comme clés pour la région, en particulier dans l’optique de la reprise de l’économie après le Covid-19. De nombreuses autres architectures ont également été proposées pour éliminer le condensateur dans la DRAM.

«Notre solution révolutionnaire aidera à abattre ce qui est appelé le « mur de la mémoire », permettant aux mémoires DRAM de continuer à jouer un rôle crucial dans des applications exigeantes telles que le cloud computing et l’intelligence artificielle», a déclaré Kar.

Lire aussi:

Mise à jour de la feuille de route pour le chip européen EPI

Craig Prunty, vice-président marketing et développement de SiPearl

SiPearl signe un contrat de licence majeur avec Arm

www.european-processor-initiative.eu/

Related articles

- BESANG LAUNCHES NON-VOLATILE DRAM

- 2D TRANSISTOR COMBINES LOGIC AND MEMORY FOR AI

- PCM, MRAM SET TO DOMINATE EMERGING MEMORY MARKET

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News